Talk:Flip-flop (electronics)

| This article is written in American English, which has its own spelling conventions (color, defense, traveled) and some terms that are used in it may be different or absent from other varieties of English. According to the relevant style guide, this should not be changed without broad consensus. |

| This It is of interest to the following WikiProjects: | |||||||||||

| |||||||||||

Flip flop or flip-flop[edit]

The correct, or at least "electronics industry-standard" terminology is "flip-flop," that is, with the hyphen. — Preceding unsigned comment added by Rcingham (talk • contribs) 03:07, 5 September 2002 (UTC)

- Chambers Science and Technology Dictionary and the OED agree with you. -- Heron —Preceding undated comment added 18:09, 6 September 2002 (UTC).

- I now replaced "flip flop" with "flip-flop" in the whole text. Should the page also be moved to "flip-flop"? We would need to first delete the redirect in the other direction in that case. Colin Marquardt 13:45, 28 Aug 2003 (UTC)

- Well, I did a cut and paste move. I couldn't find a page where I could request a move or delete the redirect. 172.196.215.224 —Preceding undated comment added 01:03, 20 September 2004 (UTC).

Circuit diagrams[edit]

Some circuit diagrams would be extremely helpful here, but I'm not qualified to draw them... can someone with a bit more knowledge of electronics put one in? Kwertii 22:13, 27 Nov 2003 (UTC)

- I will try to modify Heron's for the other types. - Omegatron 18:58, Jul 5, 2004 (UTC)

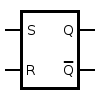

- I added the Q' for JK and SR, since they are always shown that way. T and D often are, too. We should probably add timing diagrams and NOR circuits, too, right? - Omegatron 19:31, Jul 5, 2004 (UTC)

Also, the figures of the SR latches should be consistent on whether the S or the R input is on the top or below. Ideally they should follow the text naming convention, which is SR and not RS. — Preceding unsigned comment added by Dragomang87 (talk • contribs) 12:12, 22 December 2023 (UTC)

Truth tables[edit]

I would like it to have "truth tables". I started one for RS. There are different ways of representing it, though. I have included two. Probably the explicit type is better. Feel free to remove or modify or whatever. I wanted to set the outputs apart from the inputs, though, and just made it bold for now. there is a better way, involving tables. I am going to try to do these symbols, first, though. - Omegatron 18:58, Jul 5, 2004 (UTC)

http://www.rfcafe.com/references/electrical/flip_flop_table.htm

http://poppy.snu.ac.kr/~kchoi/class/lc_intro/sequential.pdf

T flip-flop equation[edit]

The characteristic equation for a T flip-flop is given as . Should this be ? Josh Cherry 23:57, 17 Sep 2004 (UTC)

- It's not right the way it is. I don't remember what that symbol is, but if the truth table matches, then yes, change it (and remind readers like me what the symbol means, with a link to appropriate article). - Omegatron 03:38, Sep 18, 2004 (UTC)

- Looks like xor, judging from the truth table...

Internal Composition[edit]

What's inside? A Flip-flop is treated as a black box in this article. Can we add something about logic gates and transistors and describe how they allow the Flip-flop to function as it does? - Lokiskoll 09:51, Dec 17, 2004 (EST)

Different clocking types[edit]

This article does not explain the difference between flip-flops which are level sensitive (e.g. latches), master/slave, or edge sensitive. Anon April 26, 2005

- Moreover, it's totally incorrect to structure flip-flop by timing type and then by functioning type, 'cause these two are different types of classification. E.g. an RS flip-flop can be both level- and edge-triggered.

- We should first consider functioning types and then place a chapter "Level-triggered and edge-triggered flip-flops"

- btw i'm going to handle this when it's summer and i have some spare time :^) Ivan Pozdeev 15:08, 25 May 2006 (UTC)

J-K flip flop naming a myth?[edit]

A recent Slashdot post mentioned the possibility that J-K flip flops were not actually named after Jack Kilby. Does anyone buy this?

- His name will forever be engraved in the J-K flip-flop.

- This is probably an urban legend. More likely it was the initials of John J. Kardash [google.com], who in the 1950's arbitrarily used his initials on these pins on his blueprints, and it stuck.

(quoted from Slashdot post #12877710; see the Google Answers result for more information) - McCart42 (talk) 17:52, 2005 Jun 22 (UTC)

This should be fixed here as well as the kilby page and the Integrated circuits page. By fixed I mean either removed or finding some fairly reputable source for the information and citing it. Danny31415 4 July 2005 10:37 (UTC)

Presumably the above was written before the note about Dr. Nelson was added to the flip-flops page. I was at Hughes Aircraft at the same time as Dr. Nelson, and can confirm the origin there of the J-K flip-flop. Neither Kilby nor Kardash had anything to do with it.MontyPh 18:05, 10 January 2007 (UTC)Montgomery Phister

Back in 82 when I was in school, the prof claimed it was named after John Kardash. Google search (http://taracom.net/chip.pl?to=management) shows that John Kardash claims he invented the JK flip flop. I agree that the Jack Kilby surmise is unwarranted and should be removed, and at least replaced with John Kardash's version of events. One thing in John Kardash's favor is that TI was in the position to influence a lot of minds, as they sold JK flops by the bucket-load (and probably gave away nearly as many data books!). The idea that Hughes was able to establish industry-wide practice via their internal naming convention is far less plausible. Really, if it comes down to Mr. Nelson's claim vs Mr. Kardash's claim, I don't see why Mr. Nelson would get priority. —Preceding unsigned comment added by 70.253.67.240 (talk) 08:44, 24 December 2008 (UTC)

- Oddly enough, John Kardash did invent a J-K flip-flip. He has a patent on it, filed in 1965. In it, he says "One type of bistable circuit which is frequently used is known as 'J-K flip-flop'." He is not claiming to have invented the type, just that circuit. And thanks to Monty Phister, I now have an autographed copy of his 1958 textbook Logical Design of Digital Computers (he signed for me the copy of the book that my dad studied it from in 1959, to supplement the other copy I found) in which the 'J-K flip-flop' is discussed as "...has the properties of an R-S memory element, except that the combination J = K = 1 is allowed, and causes the circuit to change state...". The book mentions R. G. Nelson (probably not the Nelson he refers to above) on page 74, and discusses his logic simplification method, but doesn't say anything about the origin of the flip-flop names; I think we'll have to take Monty's word for it. Dicklyon (talk) 05:22, 24 October 2011 (UTC)

Found: Eldred C. Nelson 1953 patent filing[edit]

Eldred C. Nelson, inventor, US 2850566 "High-Speed Printing System", filed Sep 8, 1953, issued Sep 2, 1958, assigned to Hughes Aircraft Company. In column 13:

- "Each flip-flop or bistable multivibrator includes two input terminals, hereinafter termed the j-input and the k-input terminals, respectively, and two output terminals for producing complementary bivalued electrical output signals hereinafter termed Q and Qbar, respectively. Signals applied separately to the j-input and k-input terminals set the flip-flop to conduction states corresponding to the binary values one and zero, respectively, while signals applied simultaneously to both input terminals trigger or change the conduction state of the flip-flop."

Given that he's using the input names j and k, and talking about the function we call a JK flip-flop, it seems fair to credit him with the name. Dicklyon (talk) 05:56, 24 October 2011 (UTC)

In several late 1952 filings, US2823855 and US2816223, he describes the same type of flip flop, in columns 16 and 6, respectively, but without the j and k input names; just the 1 and 0 inputs. So it's fair to say he same up with JK around 1953. Dicklyon (talk) 06:08, 24 October 2011 (UTC)

Another patent at Hughes using inputs J and K refers to this 1954 pub by Nelson; I bet it's a good place to look for "JK", but I don't find it online:

@article{nelson1954algebraic,

title={An Algebraic Theory for Use in Digital Computer Design'},

author={Nelson, EC},

journal={Transactions of the IRE Professional Group on Electronic Computers},

volume={3},

pages={12--21},

year={1954}

}

- Could it be that E.C. Nelson just didn't want to start at A? (Maybe he was using A-I regularly for other pins on something he was interfacing with the JK flip-flops and didn't want to confuse them, so he felt like starting this one at J, and K is the next letter... -- or maybe didn't want his flip-flops confused with others, since the function was different, etc...) BrainSlugs83 (talk) 08:08, 19 September 2012 (UTC)

Regardless of the final outcome of the research, leaving JK unexplained is counter productive. Anyone interested in knowing what JK means will search and not find it in the page and instead find Jack Kilby with a quick Google search. So this is indirectly spreading misinformation and anyone, like I did, may be tempted to add the name to this page in order to "improve it". The correct way in the meantime is to mention the name and acknowledge the problem, maybe even directing to where one can find more information (For now I just directed to this talk page). Dragomang87 (talk) 12:20, 22 December 2023 (UTC)

Is JK flip-flop obsolete?[edit]

The JK flip-flop was widely used in the 1970's when small scale integrated circuits with flop-flops were common, and many different variants were available in TTL ICs. The advantage was that you could make counters etc. with fewer ICs. But today JK flip-flops have largely been replaced by D flip-flops because the math is simpler and they are suitable for FPGAs etc. However, I can't find any reference for this. Some textbooks are out of touch with modern electronics and still treat the JK flip-flop as important, which I think is wrong. Agnerf (talk) 11:57, 21 August 2018 (UTC)

I agree that JK FF are obsolete. I learned JK FFs at university in 1982 and have never used later. I have been working with standard cell, gate array and FPGA designs. I have know returned to university as a lecturer and am a bit puzzled that it is still part of textbooks and lectures. Svh (talk) 15:18, 12 October 2020 (UTC)

Maybe they are obsolete for standard cell, gate array, and FPGA, but they still find a use as separate ICs as a universal flip-flop (cause as the article mentions, JK flip flops can be configured to act as D-type, set-reset, and toggle flipflops), so having a few around when prototyping on a breadboard is still useful. TI's website currently lists a bunch in https://www.ti.com/logic-voltage-translation/flip-flops-latches-registers/jk-flip-flops/products.html and clicking on https://www.ti.com/product/SN74HC109 for instance shows it still listed as "Active" instead of "Obsolete".

I'm actually finding a practical use for JK flip flop ICs w/ async preset and clear (xx74xx76A) right now by using its preset to implement low-latency switch debouncing (the state changes immediately when the button is pressed regardless of any clock or microcontroller input reading capability) which then can be stable so it can be read and reset in sync with a microcontroller clock. Maybe it is considered a hobby project, but it avoids having to use an extra microcontroller pin and wasting microcontroller resources doing debouncing in software, which is important for my latency-critical application.

Em3rgent0rdr (talk) 00:02, 28 January 2023 (UTC)

T flip-flop[edit]

Could the explanation for a T flip-flop be expanded? Is Q updated every clock cycle? What does it mean "the input is strobed" - the clock or T?by Ny7K 131.111.8.102 22:59, 13 November 2005 (UTC)

- There's a sentence in the T flip-flop section that isn't even a sentence:

- A toggle flip-flop composed of a single SR flip-flop that becomes an oscillator, when it is clocked.

- I'm not sure how to fix it because I don't know what was meant. The next sentence is confusing also. I'd be for dropping that, and the next two sentences:

- To achieve toggling, the clock pulse must have exactly the length of half a cycle. While such a pulse generator can be built, a toggle flip-flop composed of two SR flip-flops is the easy solution.

- Is the single SR flip-flop implementation actually useful in any practical situation? Can someone provide a citation?

Ccrrccrr (talk) 04:09, 27 February 2008 (UTC)

- Indeed, that's lame. So I took it out. If someone figures out something to say there, put it in. Dicklyon (talk) 05:01, 27 February 2008 (UTC)

Ambiguous term?[edit]

There seem to exist at least two meanings of the term flip-flop:

- A generic term for all bistable devices, including direct latch, gated latch and edge-triggered devices

- Edge-triggered devices only. Datasheets tend to follow this convention

I believe the latter is the only correct use. Ed de Jonge 11:44, 10 March 2006 (UTC)

- The latter is the only correct term. It makes no sense to refer to something "flipping" and "flopping" without a trigger. Latches are transparent. Flip flops are semi-transparent. The page needs major updating. —TedPavlic (talk/contrib/@) 21:21, 16 July 2009 (UTC)

- I aggree the latter is "correct" in the sense that it is the convention used in datasheets, and also taught at many universities. However, this is very arbitrary, as it has little to to with technical meaning or historical usage of the words; it also seem to have resulted in widespread confusion, also in wikipedia articles - the bistable circuit called SR latch, under "latch", is exactly the same cross coupled NAND-gates as is described as a RS flip-flop in this article; other parts of the texts are carefully trying to explain the (arbitrary) distinction between the two names.

- Dare I suggest that this confusion is partially due to the tradition (in English) of assigning very,very precise meanings to simple words, instead of specifying the exact meaning by a few extra words when actual usage calls for it ? I wouldn't know for sure, as I'm obviously no native english speaker.

- However, if the edge-triggered characteristic differentiates flip-flops from latches, it would be wrong to state that the flip-flop was invented in 1919 by William Eccles and F. W. Jordan, as this circuit was built by only two triodes - a minimalistic clock-less bistable circuit - despite this, named "flip-flop". There has also been other types of "flip-flops", such as those built by relays (which sounded "flip" and "flop" as well...), long before edge-clocked devices, such as 7473 and the like, became mainstream.

- The distinctions between the common bistable elements could just as well be spelled out explicitly:

- simple SR latches

- gated (transparent) latches

- pulse-clocked (i.e. master-slave) latches

- edge-clocked latches

- All of which may have JK, D, and other variations

- The word "latch" may be replaced by words like "bistable", "register", "flip-flop", or even "memory".

- Not very surprisingly, I suggest a MERGE of the latch and the flip-flop articles.

- I also belive the article should mention that bistable elements can be built in more than one way, even if we restrict ourselves to electronics; logic gates is one way, discrete bipolar transistors another (old fashioned), and CMOS transmission gates mixed with ordinary CMOS gates, a third. - HenkeB 11:55, 9 June 2006 (UTC)

- I second that. However, the widespread convention of only referring to edge-triggered devices as flip-flops should be visibly acknowledged (maybe even within the discussion of every individual variation) to avoid confusion and (inadvertent) edit wars. Also, I have to say that I really like the term "latch" for the gated D-type since it so nicely visualizes the behavior of the circuit, "opening" to make the input visible on the output, and "closing" to "latch" the last value in place. --128.130.60.57 20:35, 23 October 2006 (UTC)

- I agree for the greater part, but the circuit you refer to as simply a "latch", is what I would call a "transparent" or "gated" latch. This is because even (so called) flip-flops have this latching function, without the transparent gating behaviour you described so nicely! /HenkeB 00:46, 15 November 2006 (UTC)

- I don't think a merge is a good idea, the pages have the potential to become pretty large (because of all the different types) and it makes sense to separate based on level-triggered componenents vs edge-triggered components. I'm trying to fix the problem, we should note the ambiguity, but choose an unambiguous way to present it on wikipedia - so that people can understand us. Fresheneesz 21:37, 3 November 2006 (UTC)

- I do not mean to be rude here, but the very term "level-triggered" is something of a contradiction, at least in this context. All digital circuits which can be triggered to go from a state A into another state B (depending on type as well as various other inputs), are triggered by the edge of some signal; they change state (or not!) at the edge, be it "latches" or "flip-flops". The term "level-triggered" could maybe be appropriate for inputs which are sampled at regular intervals, such as interrupt lines on microprocessors (i.e those which are not latching the interrupt-signal by the use of an extra flip-flop) as the word "triggered" aims at another (higher) level in this case. /HenkeB

- It isn't a contradiction. When distinguishing between edge-triggered and level-sensitive sequential circuits, one is referring to the effect of the clock on the circuit, not on any other inputs. A flip-flop is edge-triggered because the input state is only sampled on the positive or negative edge of the clock; a latch is level-sensitive because the input state is transparent to the output whenever the clock is high (or low for negative level-sensitive).Gungfusteve (talk) 15:27, 3 September 2008 (UTC)

- Ok, the same discussion once again ;) First, I was talking about the concept "level-triggered", not "level-sensitive". However, for me, your argument (I have heard it before) is nothing but an attempt to retroactively adjust improper semantics: What about bistable elements without any clock inputs (such as cross-coupled gates), are they "level-triggered" or "edge-triggered"? And what about inputs such as an interrupt line (see above)? It could hardly be called a clock. For me, it's quite simple: In a strict sense, every input that can be triggered is edge-triggered, otherwise, it's a sampled (or disabled) input. /HenkeB (talk) 01:48, 5 September 2008 (UTC)

- In case someone didn't know, an edge-triggered latch or flip-flop is basically a master-slave device which has its own circuitry for generating a very short trigger-pulse. This is to keep it open (in the sense of a level-controlled latch) for the shortest possible time, thereby minimizing the risk for analog oscillations in systems with feedback (such as state machines in computers).

- To conclude, the various basic bistable elements can be characterized as follows:

- (1) SR-latches and gated latches are controlled by static levels, but reacts (triggers) on the edges.

- (2) master-slave devices reacts internally on the first edge and externally on the second edge.

- (3) edge-controlled devices are fully controlled by one of the edges.

- That is, all types are "triggered" by the edge of a signal.

- /HenkeB 00:46, 15 November 2006 (UTC)

- The distinction between edge-triggered and level-triggered is somewhat arbitrary, but it is nevertheless important. Edge-triggered devices can only change their state on a clock edge. Level-triggered devices can change state at any point that their enable input is true. If you use a clock as the enable input to a D-latch, the state can change any time during one half of the clock cycle (and as many times as its input changes). Hence, it's transparent during that period. For a D flip-flop, no matter how many times the D input changes, the state is only updated once per clock cycle.

- It's very uncommon to see latch mean anything other than a transparent circuit or flip-flop mean anything other than a clock-edge-triggered circuit. I think the people who are trying to blur the distinction are making something out of nothing. Incidentally, SRAM is almost always made out of latches, not flip-flops (SRAM cells are synchronously controlled, but that circuitry is outside of the memory cells themselves). But I suppose that's a byproduct of the article's misleading terminology. 142.59.195.50 01:14, 30 April 2007 (UTC)

- Have you read my comments above?! As you (seem to) imply yourself, the real distinction is really between transparent and non-transparent devices (or modes); my main point is that the terms "level triggered" and "edge triggered" are semantically meaningless - you cannot trig on a static level, and a level that changes is an edge... Also, you have the problem that the first flip-flops "were" latches! /HenkeB 12:05, 2 August 2007 (UTC)

As a current Electrical Engineering student I must agree with the above statements relating that latches are not flip flops. However, it seems to be common to abuse the terms. ~~ —Preceding unsigned comment added by 71.182.247.251 (talk) 05:30, 5 February 2010 (UTC)

The article opens with "a flip-flop is a circuit that has two stable states".

I was taught that there are three types of flip-flop. A bi-stable, a monostable and an astable. — Preceding unsigned comment added by Syncopator (talk • contribs) 23:38, 13 April 2011 (UTC)

- I was taught that a flip-flop is by definition bi-stable, ie. it has two stable states. Int21h (talk) 19:31, 15 April 2011 (UTC)

I have updated the intro to reflect the difference between latch and flip-flops is either simple (transparent) or clocked (synchronous), from material in "Implementation" section. This material is important; it's why I came back to this page. ;) I am under the impression the definition is neither that simple nor well defined, so that should be noted with citations in the future. Just FYI, my impression was that flip-flops were edge-triggered or otherwise used a clock, and everything else (I'm sure with exceptions) were latches, not necessarily transparent latches. Int21h (talk) 19:31, 15 April 2011 (UTC)

Totally agree. We should drop the name "Flip-flop" and use only the terms "Latch" and "Register"(2 latch/clocked configuration). This way it would be less confusing. You don't want a designer to put a latch in a circuit when you wanted a register; So don't use the ambiguous term "flip-flop". JHBonarius (talk) 09:58, 21 November 2017 (UTC)

While it is true that historically the word "flip-flop" meant either asynchronous or synchronous, the modern usage is by far more that the word "flip-flop" is reserved specifically for synchronous while "latch" is reserved specifically for asynchronous. Out of curiousity, I looked through some old manuals, and I found for instance a 1986 RCA manual specifically uses "latch" when talking about transparent or asynchronous (https://archive.org/details/bitsavers_rcadataBooMOS_35821859/page/n113/mode/2up?q=latch) while "flip-flop" is reserved for synchronous it seems. But I don't know when exactly that distinction came about.

Anyway I edited a sentence saying that "some modern authors" distinguish by just saying "modern authors" distinguish, because I believe the general usage and consensus is to distinguish between flip-flops and latches. And I made some more edits in this article to say "flip-flops and latches" when talking about both synchronous and asynchronous types, and specifically say "latch" only when referring to only asynchronous types and specifically say "flip-flop" only when referring to only synchronous types. Some more edits can be made. Ideally if someone could pinpoint a time or decade when this distinction became common, that would be nice to add.

Em3rgent0rdr (talk) 00:44, 28 January 2023 (UTC)

New picture[edit]

No wonder its sticks out like a sore thumb, the picture was added yesterday. I added a little caption, but since the picture isn't explained, I don't even know what its supposed to represent, or where the inputs and outputs are. Not to mention the way the picture shows unconnected wires is not intuitive. It looks like its some sort of display the way it is. Like a spinning circle.. In fact thats what it could be.. but - in any case, that picture isn't at all clear. If someone could tell me where the inputs and outputs are, and what the hell it is, I could redo it so it looks much better. Fresheneesz 06:08, 13 March 2006 (UTC)

- This is a nonexisitng 'looped' circuit combined of AND-NOT (NAND) gates.

- It doesn't explain anything (moreover, it DOES confuse) so i think it should be at the end of an article about gates as an funny example, if it should be at all. Ivan Pozdeev 14:03, 14 March 2006 (UTC)

- Nonexisting? What does that mean? And looped circuit? You're not saying its representing a perpetual motion circuit are you? Sounds like this thing should be deletized. Fresheneesz 04:03, 16 March 2006 (UTC)

When a picture is next to a T-flip flop paragraph, what would it represent, a T-flip-flop maybe? So prove, that this is not a T-flip flop! And I think I added a caption, at least about the color codes. If you have a better driving signal for the T-flip-flop then a square signal, then this will be ok with me, but most T-flip-flips are used in counters and thus get a square signal!--Arnero 13:54, 23 March 2006 (UTC)

- I'm afraid most readers are going to be utterly confused by this image. Where's T, Q, and Clk? The routing through the middle doesn't make sense: it appears to be all connected together, so how is it red and blue at the same time? Try to see it from a beginner's perspective. - mako 23:49, 23 March 2006 (UTC)

- There are also T-flip-flops/clock dividers without a T input (ie, it's assumed that the output always toggles) 129.128.210.68 17:37, 1 May 2007 (UTC)

Flip-Flop definition[edit]

Flip-Flop is not a bistable multivibrator. It can implement one with peripheral components, but it is not even its main use. I would change the definition to the following: In electronics and digital circuits, the flip-flop is a pulsed digital circuit capable of serving as a one-bit memory. --Michagal 15:14, 23 May 2006 (UTC)

- I disagree, the basic RS flip flop (from which afaict all the other variants developed) is simply a bistable multivibrator implemented using logic gates rather than discrete components. Plugwash 17:58, 23 May 2006 (UTC)

- I think the problem is that the original commenter didn't look up with a bistable multivibrator was. People don't understand that a bistable multivibrator has two stable states. They see "vibrator" and think it oscillates (i.e., an astable multivibrator). A flip flop (in fact, a latch) is certainly a bistable multivibrator. —TedPavlic (talk/contrib/@) 21:19, 16 July 2009 (UTC)

Circuit diagram in D-Type Transparent Latch.svg[edit]

The diagram does not seem to be right. If the clock is zero then both outputs are 1. A correct implementation can be found e.g. at http://wearcam.org/ece385/lectureflipflops/flipflops/ , or more exactly http://wearcam.org/ece385/lectureflipflops/flipflops/fig5a.gif

I agree -- the picture of the D flip-flop is wrong (for the reasons mentioned above). The picture should be removed (and preferably corrected). -- Milom 00:16, 19 September 2006 (UTC)

SR flip flop[edit]

I don't know if there is such a thing (separate from an SR latch), but i'm putting the picture here until we have a section on an edge triggere SR latch, which i'm sure can be made. Fresheneesz 19:25, 4 November 2006 (UTC)

- There is such a thing, but it's very rare in actual use. If you take an SR flip-flop and put an inverter between S and R, then you have a D flip-flop with the "S" input becoming your "D" input. 142.59.195.50 01:17, 30 April 2007 (UTC)

- RS flip-flops would have a definite disadvantage compared with the much more common JK flip-flops, in that RS flip-flops suffer from the "forbidden" state of both R and S being simultaneously asserted on the clock edge. (I am using the convention which dictates that a flip-flop must, by definition, be a device that operates on clock edges.) If your design deliberately avoids the possibility of the forbidden input ever occurring, then a JK flip flop could be used interchangeably with the RS flip-flop; if your design anticipates that the forbidden input might occur and includes an extra layer of conditioning to translate the forbidden input into a safe alternative, then you could also just insert a JK flip flop into that overall circuit and achieve the exact same effect.

- Essentially, anywhere an RS flip-flop could be used safely, dropping in a JK flip-flop could also achieve the same effect. Since the JK flip-flop has well-defined behavior for every set of inputs, and an RS flip-flop has potentially undefined behavior, it's no surprise that JK flip-flop is heavily favored in off-the-shelf components.

- In the world of transparent latches, it is entirely possible that the RS latch's simplicity, when implemented using discrete logic, may be attractive enough to keep the design alive despite the trade-off of the forbidden input.24.222.2.222 (talk) 19:01, 21 August 2014 (UTC)

Master-slave D flip-flop[edit]

Regarding the graphic in Master-slave D flip-flop, the double NOT logic from C is quite unnecessary -- it's easier just to branch C and not one side and leave the other side normal. St.isaac 02:15, 1 March 2007 (UTC)

- Master-Slave DFF has two images: the complete implementation using logic gates and partial schematic using two D-latches. I feel that this is redundant and propose to remove the partial implementation (image on the left) and to change the central image to reflect the fact that it is composed of two D-latches with a NOT in between. Michagal 08:50, 29 March 2007 (UTC)

Master-slave terminology[edit]

Should we acknowledge that these terms are problematic? [1]. And are under review by many tech orgs & tech companies? [2] [3] [4] [5] Rich S 10001 (talk) 14:54, 13 April 2021 (UTC).

- Wikipedia is not censored. This is what the literature calls it and people who are oppressed have much more relevant things to worry about than logic diagrams. --Wtshymanski (talk) 00:22, 16 April 2021 (UTC)

- Wikipedia is not censored, but it should make an effort not to use offensive language when avoidable, which it clearly is here. This is not a discussion of slavery, where such terms may be necessary. And if by "people who are oppressed," you are referring to Black people or people of color in general, well, a fair number do object. As shown in some of the articles linked on this page. 2601:8C0:800:A177:2566:A8EF:FDCE:8D79 (talk) 20:56, 14 October 2022 (UTC)

- Here is a suggestion on how to deal with such a situation while both representing sources properly and being inclusive:

- As long as there are no new, industry-accepted terms the usage of "master" and "slave" is evaluated and different terms are used where they aren't used as technical terms but only as description (if those exist), "master" and "slave" are maybe "downgraded" to only be mentioned in quotes (as they are not actual describing a master and a slave but are only terms used in the industry)

- Once new terms emerge in reputable sources they will replace "master" and "slave" as the main names but in the beginning the "master" and "slave" terms should still be used in round brackets as "original terms" at least mentioned at the beginning of the section using the new terms so that people only knowing the original ones can understand it (and search for it)

- Once enough time is passed and the new terms are established everywhere the historical terms can be moved to a different section or even a section in the general master/slave controversy article.

- Of course these steps orient themselves on the sources, wikipedia shouldn't push the establishment of certain terms --Phoenix616 (talk) 11:37, 4 November 2022 (UTC)

- You don't have the authority to force a new replacement name on the engineering world, actually no one does, because these terms aren't defined in an official specification where some group or some company can mandate a name change. Master-Slave Flip Flop is a historical term that will never go away because millions of books and magazines have it printed in them, unless you want to start burning books to get rid of all of it. Flip-Flops aren't humans, nor are they alive, thus it doesn't matter, period. The only people that whine about this issue are spoiled non-engineers that have too much free time on their hands. 67.143.180.1 (talk) 20:48, 5 November 2022 (UTC)

- Here is a suggestion on how to deal with such a situation while both representing sources properly and being inclusive:

- Wikipedia is not censored, but it should make an effort not to use offensive language when avoidable, which it clearly is here. This is not a discussion of slavery, where such terms may be necessary. And if by "people who are oppressed," you are referring to Black people or people of color in general, well, a fair number do object. As shown in some of the articles linked on this page. 2601:8C0:800:A177:2566:A8EF:FDCE:8D79 (talk) 20:56, 14 October 2022 (UTC)

- Perhaps it would be adequate for this article to have a link to the master/slave (technology) article, and put the WP:RELIABLE sources User:Rich S 10001 mentioned in that article. --DavidCary (talk) 01:18, 16 February 2023 (UTC)

Texas Instruments dropped the usage of the master/slave terms (in at least one case), see the old datasheet of the IC CD4027B (CMOS Dual J-K Master-Slave Flip Flop) compared to the new version (CMOS Dual J-K Flip Flop). Alquantor (talk) 15:42, 10 October 2023 (UTC)

References

- ^ https://en.wikipedia.org/wiki/Master/slave_(technology)

- ^ https://www.eetimes.com/its-time-for-ieee-to-retire-master-slave/

- ^ https://www.pcmag.com/news/apple-to-remove-masterslave-and-blacklist-terms-from-coding-platforms

- ^ https://decrypt.co/32594/github-drops-master-and-slave-terms-amidst-blm-backlash-juneteenth

- ^ https://www.npr.org/2020/07/09/889502179/is-it-enough-to-remove-words-with-racist-connotations-from-tech-language-hint-no

Q[edit]

Is Q an abbreviation for something? --Abdull 15:01, 6 March 2007 (UTC)

- Welcome to the world of digital electronics! The real answer is nobody knows. Just like how nobody knows why Vcc and Vss are often used for power connections. They are merely standards that have been adopted because certain papers whom used the values become popular many many years ago.--Dacium 06:54, 5 April 2007 (UTC)

- That is not exactly true. Vcc is for collector power supply. The "c" is doubled to differentiate it from the voltage on the collector itself, Vc. Vss is used in FET transistors, "s" is for source.Michagal 13:14, 5 April 2007 (UTC)

- More specifically, CC is Common Collector—the bus tied to every collector in a purely npn circuit (not to be confused with a common collector amplifier). The other abbreviations (Vee,Vss,Vdd) were consistent and have stuck for historical reasons. Regarding Q, I don't have any sources, but I'm guessing that it was used because it's the letter before RS. That is, QRS is alphabetical (just as JK is). Additionally, Q is often used to represent the charge (or even energy) in a circuit. A flip-flop doesn't store its memory in charge (it uses positive feedback to create an unstable node that drives trajectories to its rails), but the net effect is very similar to DRAM. That being said, I'm pretty sure the QRS explanation is correct. —TedPavlic (talk) 14:54, 9 February 2009 (UTC)

- In my many years of using "VCC" I never encountered that explanation. Do you have a source for it? Dicklyon (talk) 16:27, 9 February 2009 (UTC)

- Does Wikipedia count as a source?IC_power_supply_pin --71.182.247.251 (talk) 05:45, 5 February 2010 (UTC)

- Never! 81.129.194.183 (talk) 12:40, 16 April 2021 (UTC)

- Does Wikipedia count as a source?IC_power_supply_pin --71.182.247.251 (talk) 05:45, 5 February 2010 (UTC)

- In my many years of using "VCC" I never encountered that explanation. Do you have a source for it? Dicklyon (talk) 16:27, 9 February 2009 (UTC)

- More specifically, CC is Common Collector—the bus tied to every collector in a purely npn circuit (not to be confused with a common collector amplifier). The other abbreviations (Vee,Vss,Vdd) were consistent and have stuck for historical reasons. Regarding Q, I don't have any sources, but I'm guessing that it was used because it's the letter before RS. That is, QRS is alphabetical (just as JK is). Additionally, Q is often used to represent the charge (or even energy) in a circuit. A flip-flop doesn't store its memory in charge (it uses positive feedback to create an unstable node that drives trajectories to its rails), but the net effect is very similar to DRAM. That being said, I'm pretty sure the QRS explanation is correct. —TedPavlic (talk) 14:54, 9 February 2009 (UTC)

- That is not exactly true. Vcc is for collector power supply. The "c" is doubled to differentiate it from the voltage on the collector itself, Vc. Vss is used in FET transistors, "s" is for source.Michagal 13:14, 5 April 2007 (UTC)

Volatile memory[edit]

Note that it is just to store data temporarily, this type of memory formed by the flipflops is volatile which means that it depends on voltage —The preceding unsigned comment was added by 202.83.169.218 (talk) 06:14, 3 May 2007 (UTC).

Additional information (correction) about SR FFs and news about JK FFs[edit]

A lot of articles has been written about SR flip-flops. Although the SR flip-flop is very simple, I have read some wrong conclusions. Very often it is forbidden to connect both inputs S and R simultaneously with 1-signal (NOR-gates used), or in other cases the status of the flip-flop is called 'unstable'. In my opinion this is wrong. The only consequence is, that this status cannot be stored. There is only one problem if S and R get a 0-signal simultaneously after S and R has received a 1-signal before. In this case it is indefinite which state will follow (Q=1 or Q=0). Especially this 3rd status of a SR flip-flop makes it possible to create ideal pulse circuits to pulse flip-flops (normally RC combinations are used) for instance. The usage of such ideal pulse circuits can be a basis to construct non clocked JK flip-flops

Perhaps it might be necessary in future to differ between edge-triggered clock and other inputs.

Please find the details and diagrams of ideal pulse circuits and non clocked JK flip-flops in an article "Ideal pulse circuit without RC-combination and non-clocked

JK flip-flop"

on my homepage below.

http://www.hpc-berlin.de/dokumente/flipflop_en.pdf

--Klaus-Eckart 12:51, 13 September 2007 (UTC)

- This topic seems to come up a lot on the talk page. This is a page on flip flops, not latches, and so it should describe flip flops. RS flip flops are unstable with . RS latches are not (unless moving from to quickly). It's the "flip" and "flopping" that sets up the instability in the flip flop. Such "flipping" and "flopping" doesn't exist with the latch. The solution is to stop calling latches flip flops (i.e., show the difference between asynchronous and synchronous inputs/outputs). —TedPavlic (talk/contrib/@) 21:16, 16 July 2009 (UTC)

- Unfortunately, I read the article until today.

I hope to understand you correctly. - Please have a look only at the circuit of a (NOR) RS flip-flop and forget that it is said RS flip-flop with its described properties. And now you think what happens is if R = S = 1. It´s clear -> both outputs are 0!. Do it in practice -> the same result! No instability! Have a look at my article, there can you find now a very simple simulation of the non-clocked JK flipflop. It consists of 5 RS flipflops. You can see quite well that the state at R = S = 1 (NOR) is not at all unstable. This state is stable and usefull.

- What causes such a statement - instability?

This statement 'instability' does not describe the characteristics of the circuit. It's just a definition, allow only input assignments that can be saved. This restricts the properties of the actuell circuit but a lot.

What do you think? - What is better, to define the same circuit with different names and different properties, or the RS flipflop in all its complexity to describe?

- By the way, with a latch that has nothing to do.--Klaus-Eckart (talk) 10:24, 19 January 2010 (UTC)

- Unfortunately, I read the article until today.

Timing and metastability[edit]

Under "Timing and metastability", this line "In many cases, metastability in flip-flops can be avoided by ensuring that the data and control inputs are held constant for specified periods before and after the clock pulse, called the setup time (tsu) and the hold time (th) respectively." is a bit unclear and ambiguous. I first thought tsu and th was the time the flip-flop waited before it accepted any input. So "the data and control inputs" refers to _external_ drives? Should the sentence be reformulated? 129.241.203.41 12:14, 11 October 2007 (UTC)

- I agree. The metastability can be avoided in ``all cases``, not ``in many cases`` by observing Ts and Th. The definition of tsu and th is the specified time flip-flop's input has to remain '0' or '1' before and after clock's active edge. Michagal 12:32, 11 October 2007 (UTC)

Edge-triggered D flip-flop[edit]

I was wondering how the picture below is positive edge triggered. When the signal changes from high to low the data is stored, not when it changes from low to high. Is the clock signal inverted? If so, it should be stated that the picture is negative edge triggered.

No, the diagram is fine. Note that when the clock signal is low, both the lines leading out of the first stage (the four gates on the left) into the second stage end up high, regardless of whether D is high or low. And the second stage is a SR latch which is set/reset by sending one of its inputs LOW, so nothing changes when both are high. Only when the clock switches to high with the data input held stable do the lines to the output latch go low (only one of the lines), as is necessary for it to change. (it's important for D to stay at one value during the transition, otherwise there are logic races and the results are unpredictable) 88.107.18.45 (talk) 06:57, 29 December 2008 (UTC)

Gate bias[edit]

The article does not explain the historical bias/suitability of NAND gates over AND, OR, XOR, NOR and XNOR to implement flip-flops.Anwar (talk) 17:26, 22 May 2008 (UTC)

This is covered in the article on NAND gates. They happen to be simpler than the others when implemented in DTL and TTL. In RTL, on the other hand, NOR gates are easier and NAND is hard. —Preceding unsigned comment added by 60.241.12.136 (talk) 10:50, 2 September 2009 (UTC)

The revision on 15:01 5th Jan 2011 by Wtshymanski changes the sentence that previously said that NAND is easier than NOR in DTL and TTL, to say that it is also easier in CMOS too. But NAND and NOR in CMOS look similar to me, so I can't see why CMOS NAND is would be easier that CMOS NOR.

60.241.12.136 (talk) 11:03, 3 June 2011 (UTC)

CMOS NAND is "easier" because n-FETs have better performance than p-FETs, and the NAND has the good FETs in series rather than the bad ones. 81.229.81.239 (talk) 22:16, 1 April 2012 (UTC)

Practical considerations[edit]

Maybe is should be noted, that most flip-flops also have asyncronous preset and clear possibilities,have enable, and if disabled both output go HiZ. Bg665 (talk) 20:10, 21 October 2008 (UTC)

JK flip-flop mistake?[edit]

Hello,

At the beginning of the "JK flip-flop" section it reads:

The JK flip-flop augments the behavior of the SR flip-flop (J=Set, K=Reset) by interpreting the S = R = 1 condition as a "flip" or toggle command.

This is a JK flip-flop, so shouldn't it say:

The JK flip-flop augments the behavior of the SR flip-flop (J=Set, K=Reset) by interpreting the J = K = 1 condition as a "flip" or toggle command.

This is an important distinction as it would confuse me to see S = R = 1 in the introduction sentence and then to read the Characteristic table, which has J = K = 1 for the flip.

I was too nervous to just go ahead and change it myself. Does anyone else agree that it needs to be changed? fogus (talk) 20:27, 3 December 2008 (UTC)

- It makes sense to use S and R in that sentence. It is making a comparison with an SR flip-flop so SR terms should be used. If you jump straight to J and K the logic of the comparison becomes less obvious, and arguably wouldn't make sense at all - the sentence begins with an SR flip-flop and modifies it to be a JK flip-flop. Using JK nomenclature to begin with would fuzzy the fact that we start with an SR type. CrispMuncher (talk) 22:50, 3 December 2008 (UTC)

SR Flip-flop Truth table[edit]

When , the output isn't undefined, but 0 in both and . --Unsigned (at least as of February 9, 2009)

- It's a race condition. There's a better discussion at latch (electronics). Depending on which delay is shorter, the output will either be 1 or 0. There's no way to predict it. —TedPavlic (talk) 14:47, 9 February 2009 (UTC)

- To be more precise, in an edge-triggered SR flip-flop (NOT LATCH!), if on a clock edge, the flip flop output will be undetermined. Similarly, as discussed on the latch (electronics) page, moving quickly from a non-restricted state to and then back to leads to a race condition where the output of the latch is undefined. Of course, the flip flop page should be modified to prevent this confusion. Taking latch-specific information off of the edge-triggered flip flop page would go a long way to clearing up the confusion. —TedPavlic (talk/contrib/@) 15:47, 16 July 2009 (UTC)

- The section you edited is about the latch (cross-coupled NOR gates, it says). A latch is a flip-flop, too. I'm not familiar with an edge-triggered SR flip-flop; do they exist? Dicklyon (talk) 16:00, 16 July 2009 (UTC)

- An edge-triggered RS flip flop (the combination of two clocked RS latches) is commonly used to motivate the design of the edge-triggered JK flip flop. A quick search of Google and a random click leads to [1] which uses the edge-triggered RS flip flop as a tool to discuss the race condition that can occur (and then uses the JK flip flop as a solution). Most digital texts...

- First introduce the SR latch.

- Next introduce the clocked SR latch (i.e., SR latch with AND gates in front and a "clock" input).

- Next introduce the edge-triggered SR flip flop.

- Next introduce the edge-triggered JK flip flop.

- Add combinational logic to describe D and T flip flops.

- I'm ASSUMING that this page was originally laid out to do something similar than that, but since then it's become a mess. The section marked "RS flip flop" should maybe be removed or restructured so that there's no ambiguity that it's describing a flip flop and not a latch (the distinction is important, especially for asynchronous designs). A better solution would be to move the "master–slave" D flip-flop section ahead of all the others as an example of the general flip flop topology. Heck, maybe a better solution would be to reorganize following the conventional outline above. —TedPavlic (talk/contrib/@) 21:23, 16 July 2009 (UTC)

- An edge-triggered RS flip flop (the combination of two clocked RS latches) is commonly used to motivate the design of the edge-triggered JK flip flop. A quick search of Google and a random click leads to [1] which uses the edge-triggered RS flip flop as a tool to discuss the race condition that can occur (and then uses the JK flip flop as a solution). Most digital texts...

- The section you edited is about the latch (cross-coupled NOR gates, it says). A latch is a flip-flop, too. I'm not familiar with an edge-triggered SR flip-flop; do they exist? Dicklyon (talk) 16:00, 16 July 2009 (UTC)

- To be more precise, in an edge-triggered SR flip-flop (NOT LATCH!), if on a clock edge, the flip flop output will be undetermined. Similarly, as discussed on the latch (electronics) page, moving quickly from a non-restricted state to and then back to leads to a race condition where the output of the latch is undefined. Of course, the flip flop page should be modified to prevent this confusion. Taking latch-specific information off of the edge-triggered flip flop page would go a long way to clearing up the confusion. —TedPavlic (talk/contrib/@) 15:47, 16 July 2009 (UTC)

- That search bolsters my impression that there's no such thing, except as a pedagogical tool. Anyway, most RS flip flops are latches or even simpler cross-coupled gates; those are still flip-flops, traditionally. I'm not sure what the intention of this page's organization was, but I agree that it's worth trying to clean up; but not by being narrow in intepretatin of terms, or making changes incompatible with the text of a section. Dicklyon (talk) 00:46, 17 July 2009 (UTC)

In the 15:56 16July09 edit, the excitation table was changed to indicate a race condition when Q(t) and Q(t+1) are both one (ie Q remains high). I believe the previous incarnation (at 15:54) was correct, the race condition is properly shown in the characteristic table when R and S are both 1. --P.Gilmore —Preceding unsigned comment added by 64.136.252.140 (talk) 13:58, 25 November 2009 (UTC)

Most of this page fits better under "latch" category[edit]

The discussion of "transparency" on this page is poor. It would be better to enhance the latch page with a full description of transparent, transparent-high (opaque-low), and transparent-low (opaque-high) latches, and then use that discussion to motivate the introduction of an edge-triggered device. That edge-triggered device is (now) conventionally called a "flip-flop."

This page as it stands mentions briefly the modern naming convention and then goes on to discuss topics that make more sense under the "latch" category.

So I suggest making this page a pure flip-flop page (in the clocked sense of the term) with references to latch. Detailed discussion of gates and transparency can be handled there. —TedPavlic (talk) 14:45, 9 February 2009 (UTC)

- I'm against purity here; I'd rather see the article be inclusive of all things called flip flops. It could be done summary style, with links to in-depth pages on latches, on edge-triggered flip-flops, etc., if that would address your concerns. Dicklyon (talk) 00:38, 17 July 2009 (UTC)

- Yeah, latch and flip-flop need to be a lot more clear here. I don't know of a textbook released in the last 5 (10?) years that calls the edge triggered device anything other than a flip-flop and a level sensitive device anything other than a latch... Hobit (talk) 02:14, 12 October 2009 (UTC)

- 5-10 years is "nothing", flip-flops has been around for almost 100 years! Just following the latest textbooks would be plain recentism. 83.255.38.46 (talk) 09:23, 25 August 2010 (UTC)

- I'm not sure what terminology '46 would like to see. For an example of a patent that uses "latch" for level-sensitive circuits, see U.S. Patent 3,783,254. I believe this was one of the early patents for the level-sensitive scan design that has been used in IBM mainframes for decades. Jc3s5h (talk) 16:35, 25 August 2010 (UTC)

- I like latch as well, "flip-flop" sound a little cheesy in my ears ;) However, the terms seemed to be more or less interchaneable in English usage for a very long time, until someone (who?) decided to try to reserve flip-flop for master-slave devices - despite very early historical usage of this term for simple transparent devices (see recently removed info in the article, for instance).

- BTW, in my own native language, Swedish, we typically use the term vippa for all kinds of multivibrators, and specify "transparent" etc as needed; I belive the same principle is used in many other languages, such as German, French, and others. 83.255.38.46 (talk) 00:33, 26 August 2010 (UTC)

- 5-10 years is "nothing", flip-flops has been around for almost 100 years! Just following the latest textbooks would be plain recentism. 83.255.38.46 (talk) 09:23, 25 August 2010 (UTC)

- Yeah, latch and flip-flop need to be a lot more clear here. I don't know of a textbook released in the last 5 (10?) years that calls the edge triggered device anything other than a flip-flop and a level sensitive device anything other than a latch... Hobit (talk) 02:14, 12 October 2009 (UTC)

- We do something like that in English, traditionally, with "transparent" modifying either "flip-flop" or "latch". A book search shows 8 books with "latch is a flip-flop", and 5 with "flip-flop is a latch". The distinction is modern, promulgated primarily by the terminology that TI chose for their TTL family around 1969. It's clear that "flip-flop" is still a common generic term that includes transparent ones, two-phase ones, etc., in spite of narrower uses at the same time. Dicklyon (talk) 05:13, 27 August 2010 (UTC)

- I tried to hint on this difference between original and "modern" usage, but you actually removed those text snippets (if I remember correctly). I guess that you perceived it as some kind of propaganda for this "modern" usage, despite its intention to clarify and illustrate the confusion that arises from hijacking a broad generic term like latch or flip-flop for a narrow specific meaning. I still belive there would be neat with, say, a paragraph called terminology, clarifying this. I also still feel these two articles should be merged (although sub-categories like set-reset, transparent, clocked, etc could have their own detailed articles, if needed). What do you say? 83.255.34.43 (talk) 11:47, 1 September 2010 (UTC)

I was a sophomore at MIT in 1991 and the usage "latch" for transparent and "flip-flop" for edge-triggered was already standard in the EE(CS) dept at the time. — Preceding unsigned comment added by 81.229.81.239 (talk) 22:18, 1 April 2012 (UTC)

D flip flop missing reset behavior[edit]

It would be nice if the D flip flop spoke of reset signal behavior or had it in the truth table. Is reset read on clock edge? Is it async? —Preceding unsigned comment added by Brandon.irwin (talk • contribs) 01:42, 12 December 2009 (UTC)

- Typically Reset is read asynchronously but it dosen't have to be. Rester might be better explained with a cirucit level diagram, perhaps I'll add one... Guerberj (talk) 05:46, 13 December 2009 (UTC)

I think that D Flip Flop needs better explanations. And also, I need to point that there is no explanation about the Set Signal. —Preceding unsigned comment added by 94.54.32.255 (talk) 22:12, 6 January 2010 (UTC)

Is it standard for D-type pins labeled R and S to be synchronous and pins labeled CLR and PRE to be asynchronous? In Xilinx's ISE software, there are separate packages for each type[1]: FDRS (synchronous Reset/Set) and FDCP (asynchronous Clear/Preset). Should it be explicitly stated that the synchronous form requires an appropriate clock edge to update Q, whereas the asynchronous is immediate?

References:

--24.231.250.224 (talk) 12:24, 24 October 2011 (UTC)

JK flip-flop[edit]

I think there's a little discrepancy in the JK flip-flop section. The timing diagram is for a positive edge triggered JK flip-flop, and the article states "The flip-flop is positive-edge triggered (rising clock pulse) as seen in the timing diagram." This is true, but the circuit symbol diagram shows a negative edge triggered flip-flop(clock connection arrow pointing inwards) which could cause some confusion among readers.130.209.241.193 (talk) 09:13, 20 January 2010 (UTC)

I changed the image description to reflect this. This is my first article edit, so if there's any problems or issues don't hesitate to contact me. Also, the JK flip flop description seems to suggest that all JK flip flops are positive edge triggered, which is not the case. Although this may be simply my perception of what is stated, so I haven't changed anything else. I created a Wikipedia account just after detailing the original issue, hence why i'm signing this edit with my screen name and not IP address. Darth Gazak (talk) 09:31, 20 January 2010 (UTC)

STL Scripting[edit]

I'm not used to editing wiki and all so ill apologize for not signing this up ahead, Scripted a small flipflop in stl, for anyone that wants to write one, or has to write one, instead of using an LAD or FDB.

Every x value not preceeded by an comment should be in the same byte range pick one to your own liking I have used the 22th byte range in two or three places, but thats changable.

A(

O Q x.7

O Q x.4

)

NOT

= Q x.0

A Q x.0

= L 22.0

A(

A(

A(

A(

O L 22.0

ON I x.0

// The above is your input, every input is the same ofcourse.

)

NOT

= Q x.1

A Q x.1

O Q x.6

)

NOT

= Q x.2

A Q x.2

O I x.0

// The above is your input, every input is the same ofcourse.

)

NOT

= Q x.3

A Q x.3

O Q x.0

)

NOT

= Q x.4

A Q x.4

= L 22.1

A(

A(

A(

O L 22.1

ON I x.0

// The above is your input, every input is the same ofcourse.

)

NOT

= Q x.5

A Q x.5

O Q x.2

)

NOT

= Q x.6

A Q x.6

O I x.0

// The above is your input, every input is the same ofcourse.

)

NOT

= Q x.7

A Q x.7

= Q x.7

A L 22.1

BLD 102

= Q x.0

// replace x with an output digit.

A L 22.0

BLD 102

= Q x.1

// replace x with an output digit.

A few minor mistakes, since i took it straight from the program im running, but i fixed them. 217.166.79.130 (talk) 09:44, 10 February 2010 (UTC)

D flip-flop - Logic Table[edit]

It schould be "Rising Eadge or 1" right? http://web.cs.mun.ca/~paul/cs3724/material/web/notes/node13.html http://www.elektronik-kompendium.de/sites/dig/0210031.htm (German) sorry for bad english, don't want to be unpolite -- please help —Preceding unsigned comment added by 194.95.66.1 (talk) 21:54, 3 May 2010 (UTC)

D (Data) flip-flop[edit]

This section has a problem with the last paragraph/block, which doesn't match the figure (4-bit shift register), so it doesn't make sense:

- The above circuit shifts the contents of the register to the right, one bit position on each active transition of the clock. The input X is shifted into the leftmost bit position.

There is no x input in the figure, and the bits look like they're shifting rightward, which is not necessarily the leftmost bit position. —Preceding unsigned comment added by 76.221.133.164 (talk) 07:22, 22 November 2010 (UTC)

Chaos[edit]

What happened to the section on Chaos? I'm gona go ahead and restore it. --Aminhungryboy (talk) 17:40, 29 November 2010 (UTC)

- It is too abstract for this essential and concrete page about flip-flops. Please, place this data on a more appropriate page. Circuit dreamer (talk, contribs, email) 17:46, 29 November 2010 (UTC)

- I see what your saying. I'm not the most experience wikipedia user. Do you know a page in which I may insert this? --Aminhungryboy (talk) 17:51, 29 November 2010 (UTC)

- Maybe, as an application of a Chaos theory or Chua's circuit? Circuit dreamer (talk, contribs, email) 18:25, 29 November 2010 (UTC)

- Hmm, Chaos theory page seems like a good idea. The stuff on Chua's circuit was just a bit of a background on simple chaotic circuits. I'll move it to the chaos theory page once I get the time. Thanks. --Aminhungryboy (talk) 19:57, 2 December 2010 (UTC)

Clock[edit]

Should the lead contain a flat-out statement that flip-flops are clocked? The statement is watered down later in the article with the discussion of simple flip-flops, but the lead is not strictly correct as it stands. Jc3s5h (talk) 18:06, 29 November 2010 (UTC)

- We have somehow to distinguish a flip-flop from a latch to justify the presence of the two articles. For this purpose, we have to subordinate the second article to the first one. So, we have to present the flip-flop as something more complicated than a latch. From this viewpoint, a flip-flop is a latch + something else; it is a latch + some gating mechanism. In the lede, we have to name somehow briefly this additional input circuitry (e.g., "clocked" or "edge triggered" inputs) to distinguish the flip-flop from a latch. Circuit dreamer (talk, contribs, email) 18:43, 29 November 2010 (UTC)

- The reference at Latch (electronics) (http://rfic.eecs.berkeley.edu/ee100/pdf/lect24.pdf) suggests that the distinction between a latch and a flip-flop is whether it's transparent or not, i.e. whether it's edge-triggered or level-triggered. I suspect that depending on where you look, you'll find different definitions, so I don't think we should be constructing the article in such definitive terms. Oli Filth(talk|contribs) 19:38, 29 November 2010 (UTC)

- This topic is discussed many times on this page but I would like to note that transparent and level-triggered are not always equal. A level-triggered (gated) latch becomes transparent if we hold the enable input active for long enough. It becomes almost "edge-triggered" if we hold the enable input active only for a moment and this is the use of the level triggering. The most elementary latch (the basic bistable circuit) is permanently transparent; a level-triggered latch is transparent for a short time; an edge-triggered latch is transparent for an extremely short time; a master-slave latch is not transparent at all (it behaves as a "canal lock" or a "lock-out chamber").

- I agree that we should not base the article on such definitive terms. IMO we may distinguish flip-flops from latches, particularly in the lede, by using a more general word as "synchronization". From this viewpoint, a latch is an asynchronous bistable circuit while a flip-flop is a synchronous bistable circuit; i.e., a flip-flop is a synchronized latch. Circuit dreamer (talk, contribs, email) 22:25, 29 November 2010 (UTC)

Many flip-flops are not clocked, and may be used in asynchronous circuits. I reverted this major redefinition. Dicklyon (talk) 04:39, 30 November 2010 (UTC)

- No, you have not simply reverted this major definition; you have brutally reverted all my edits... Your behavior is insulting, uncivil and provocative... I have not expected it... I am surprised... I am amazed...

- If you think that "a flip-flop is a circuit that has two stable states and can be used to store state information", I will say to you that this is exactly the definition of the fundamental bistable circuit that you have removed...; this is exactly the definition of a latch... You have to add something more to make it a flip-flop definition...

- I have restored the essential data about fundamental ideas behind bistable circuits, latches and flip-flops. I invite thinking wikipedians to join this extremely interesting discussion to improve the fundamental article about these legendary memory elements. Circuit dreamer (talk, contribs, email) 06:38, 30 November 2010 (UTC)

Rearranging "Flip-flop" and "Latch" articles[edit]

I have moved the introductory part of this article to Latch and rearranged the two articles guided by the considerations below.

- Flip-flop and latch are not the same; so, they deserve separate pages (as it is).

- Flip-flop and latch are closely related; so, the two pages have to be closely related as well.

- The latch precedes chronologically the flip-flop.

- Eccles and Jordan have invented a latch, not a flip-flop; so, the data about their patent have to be placed on Latch.

- The fundamental bistable circuit is simpler than a latch and the latch is simpler than a flip-flop; so, the fundamental bistable circuit has to be inserted in the introductory part of Latch.

- The flip-flop is based on the latch; it is built by one or more latches; so, Flip-flop is a continuation of Latch.

I would be glad if you appreciate my efforts to solve the problems connected with the distribution of the contents between the two pages. Circuit dreamer (talk, contribs, email) 22:53, 1 December 2010 (UTC)

- OK, I've made an effort to help, by resetting to a less wrong state and starting a formal merge discussion. Your assertion that "Eccles and Jordan have invented a latch, not a flip-flop" is pure revisionism, not supported by sources; not a good basis for your way of fixing the problem. I think the merge that Zen-In suggested will make it easier to get it right, with flip-flop as the broad category, and things like transparent latches and clocked D flip-flops as subtypes. Dicklyon (talk) 06:15, 4 December 2010 (UTC)

No new Science here[edit]

There is no need to develop a new taxonomy of latches and flip-flops. In fact it might be a good idea to merge the two pages since there is lot of cross-over between the two. There are clocked latches and flip-flops can be used asynchronously. It is better to have an accurately written article instead of trying to write the articles in such a way as to justify having two separate pages as C-D wants. But these same opinions have been voiced many times before by myself and others for a couple of years. At this point I think the only solution is to file an ani action and see how the chips fall. Zen-in (talk) 05:36, 2 December 2010 (UTC)

Why the big change?[edit]

I don't see support for Circuit Dreamer's wholesale redefinition and reorganization of the article since Nov. 28 or so, and propose that we take it back again to where it was before, and discuss changes before committing to something so major. To me, the old broad definition makes a lot more sense than the new narrow one. Perhaps as others have suggested, merging latch in here will also make it easier to start with the broad definition and then define narrower usages. Dicklyon (talk) 23:27, 3 December 2010 (UTC)

- I think I support the notion of merging down to a single article. The distinction between latches and flip-flops is largely academic, and certainly ill-defined. Oli Filth(talk|contribs) 23:55, 3 December 2010 (UTC)

- tentative support for merge. See Dicklyon's comments from a year ago. Transistor bistable multivibrators were called FFs. Today's distinction is more tied to choice of clocking scheme (which driven by underlying technology). Tentative because merge may cause bloat. Glrx (talk) 03:57, 4 December 2010 (UTC)

- There's not so much there that the result will be huge. We may even get some de-bloating in the merge. I just looked at latch (electronics) and saw the "Latch schematics from the Eccles and Jordan patent filed 1918" which is just absurd. In Google book search, there are 381 hits for "Eccles Jordan flip flop", but nothing at all for "Eccles Jordan latch". This revisionism of Circuit Dreamer based on what he thinks things should be called is just annoying. Dicklyon (talk) 06:03, 4 December 2010 (UTC)

Merge proposal[edit]

- Merge from Latch (electronics) into Flip-flop (electronics)

I've added merge proposal tags and opened this discussion, in support of the idea floated above. A latch is just a type of flip-flop, in modern terminology, and can easily be treated with sections in the main article, which will remove much of the imagined problem that is being addressed wrongly by trying to give a narrower definition to flip-flop. Dicklyon (talk) 06:13, 4 December 2010 (UTC)

Seeing no objection, I've made a first cut at a merge, based on the version before Circuit Dreamer's redefinitions. Can we work from there? Dicklyon (talk) 01:38, 5 December 2010 (UTC)

- There were three possible solutions of the problem: two separate pages; one big page; one main page and a few subpages. As I can see, you have chosen the second one. I appreciate your efforts to improve the article and will await you to finish your edits. For now, I would like only to note that a T flip-flop made from a synchronous edge-triggered D flip-flop by connecting its inverted output to its D input is exactly an asynchronous circuit. There is a clever trick in this circuit solution: the genuine D input is used as an internal input for implementing a delayed (with one cycle) "negative feedback" and the clock input is used as a new circuit input. As a result, the circuit has lost the clock input; it has only one asynchronous input. Circuit dreamer (talk, contribs, email) 16:35, 5 December 2010 (UTC)

- I suppose by some definitions you can call it asynchronous. But it's also a device commonly used in synchronous clocked systems to make an alternating 0-1 signal. The output changes after the after clock edge, just as with other synchronous flip-flops; it integrates perfectly with the others, since it is one. If you want to use it as an element in an async circuit, say by clocking it with a data signal, you can do that, too. Dicklyon (talk) 20:22, 5 December 2010 (UTC)

- It can be used in synchronous clocked systems but it is an asynchronous T flip-flop. If we consider it as a D flip-flop with D input connected to some output (in this specific case, to its own inverted output) and C input connected to the clock, it is a synchronous D flip-flop having two inputs (data and clock). But in this circuit the D flip-flop is only a component used to build a T flip-flop having only one input (toggle). So, the whole circuit is an asynchronous T flip-flop that can be used wherever. Circuit dreamer (talk, contribs, email) 21:33, 5 December 2010 (UTC)

The "mess" is restored again...[edit]

I am glad to see that you have arrived at the decision to merge the two pages since it actually was my idea. As you can see, I have only distributed the existing contents between the two pages and structured them to prepare the ground for future merging (if we decide to do it). Now the two pages are tidy, well structured and intelligible. The fundamental idea is revealed in the beginning of Latch and then its evolution is shown in a logical succession: basic bistable circuit -> "direct" RS latches -> gated latches -> ... then it continues in Flip-flop ... -> edge-triggered flip-flops -> pulse-triggered flip-flops. Now, we have only to insert the contents of latch page in the beginning of flip-flop one and to generalize the lede to obtain the desired common page (latch should be redirected to flip-flop).

Of course, it is obvious for everyone that now latches and flip-flops are unnaturally separated in these two pages; they are only different stages of the humble Eccles-Jordan bistable circuit in the stairs of its evolution. But we have somehow to distribute the content about all these memory circuits into separate pages because it is too large for one page. So, I have started with the existing organization - each circuit in its own page, subordinating the latch to flip-flop page. But this is only one possible (not so bad) way of presentation.

The alternative approach (suggested above) can be realized as a set of one main and a few subordinated pages. The main flip-flop article should contain only essential data about fundamental bistable circuit and to show (in the succession above) the typical flip-flop implementations. The specific circuit solutions should be shown in the separate subpages. Thus the main page will reveal the fundamental ideas behind flip-flops and the subpages will show their specific implementations (see for example op-amp applications).

I hope you realize how arduous this undertaking is. It can be implemented by creative, thinking and conscientious wikipedians behaving positively; but I do not see such persons here. Instead, I see exactly the opposite - wikipedians that brutally blank, remove and revert without any comments large blocks of text revealing the fundamental ideas behind circuits...

I was rather impressed by wikipedians (some of them anonymous) having a talk more than a year ago. There are valuable thoughts, generalizations and philosophy in their discussions that can be inserted in the articles. Such kind of people can implement this ambiguous undertaking... but they keep silence for now... Maybe new people will join this undertaking... Till then the reorganized articles about latches and flip-flops can serve as a better basis for further improving (merging, splitting, whatever...) than the previous eclectic "mess". Circuit dreamer (talk, contribs, email) 11:16, 4 December 2010 (UTC)

- The fundamental problem is that the flip-flop article is built around the most broad and generic definition of the term, and you can't just change that without consensus. The Eccles Jordan trigger circuit was called a flip-flop long before the notion of a "latch" was invented for some kinds of flip flops. You can still represent the more modern distinctions of usage in the article, but you can't use that to rewrite history. Dicklyon (talk) 19:19, 4 December 2010 (UTC)

- Well, another solution of the problem is to add a small introductory text in the beginning of flip-flop page (e.g., in History or/and Implementation section) where to make the connection with the simpler latches (to remind the Latch page). This text will serve as a summary about latches. Circuit dreamer (talk, contribs, email) 21:50, 4 December 2010 (UTC)

removing section: Gated T Latch[edit]

I'm going to remove the following section from the article because there are no inline sources for it and it is unclear to the point of being useless. Before this information can be useful, several questions must be answered.

- What does it mean when the clock input is "strobed?" Does it mean that the clock is on its rising edge, off, or on?

- What happens when the clock input is not "strobed?"

- What is the relationship between Qnext and Qprev in terms of time?

- Does "If the T input is low, it holds the previous value." apply when the clock input is "strobed" or does that statement apply always?

Also, the ending sentence of this section is redundant with the other sections of this article so it is also being removed. --Sbluen (talk) 05:38, 1 January 2011 (UTC)

====Gated T latch==== This is another synchronous SR latch that toggles the previous output. If the toggle (T) input is high, the T latch (well known as T flip-flop) changes state ("toggles") whenever the clock input is strobed. If the T input is low, it holds the previous value. Characteristic equation is; Qnext = T ⊕ Qpre, where Qnext is the next state and Qprev is the previous state.

| T | Qprev | Qnext | Comment |

|---|---|---|---|

| 0 | 0 | 0 | Hold state |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | Toggle state |

| 1 | 1 | 0 |

A T flip-flop can also be built using a JK flip-flop (i.e., with T implemented by connecting J & K pins together) or D flip-flop (T input and Qprevious is connected to the D input through an XOR gate).

Earle latch needs a diagram[edit]

I think I'd prefer a neatly hand-drawn sketch, scanned, instead of "ASCII art". This isn't Usenet 1983, and the ASCII picture takes too much interpretation to make it useful (and I suspect is missing some lines, too). Will anyone beat me to fixing it? --Wtshymanski (talk) 19:24, 5 January 2011 (UTC)

'Gated SR latch' error[edit]

I think there's an error under the heading 'Gated SR latch'. This seems wrong for the gates mentioned: "The extra gates further invert the inputs so the simple (not)SR latch becomes a gated SR latch (and a simple SR latch would transform into a gated (not)SR latch with inverted enable)." I believe that using ANDs on an SR latch turns it into a gated SR latch, and NANDs for a (not)SR latch turn it into a gated (not)SR latch. What it should say is that ANDs on a (not)SR latch and NANDs on an SR latch invert them into gated latches. I think the article says it backwards. But I don't have electronics experience, so someone tell me if I'm wrong. LieAfterLie (talk) 07:18, 13 January 2011 (UTC)

Uses[edit]

This section is a random collection of observations/facts. Some of those observations are suspect and some suggest bad practice. Why should we worry about building a gated transparent latch out of edge triggered FFs? Is it a good idea to build a negative edge triggered FF out of an inverter and a positive edge triggered FF? Yes, a chain of T FFs makes a frequency divider, and that technique is used in low power applications such as satellites and watches, but it would not be used in low phase noise PLLs. Glrx (talk) 20:31, 28 January 2011 (UTC)

- I agree, it does seem like a random collection of observations/facts. I though the part about level-sensitive latches causing design-for-test problems was curious. I suppose it's true if you only have one clock. But if you have a master-slave arrangement of level-sensitive latches, with one clock for the masters and another for the slaves, the two clocks being non-overlapping, then you have Level Sensitive Scan Design, which was created to make design-for-test easier. In the foundry I worked, customers would send in designs with edge triggered flip-flops, and they would be replaced with LSSD because they could be tested more effectively. At the time, in the early 2000s, the customer's software had a hard time with LSSD so fake virtual flip-flops were provided for them to use in their software, and they were replaced before the final physical design was done. Jc3s5h (talk) 21:12, 28 January 2011 (UTC)

- The W. Wallace McDowell Award article makes it sound like the level-sensitive scan design that Jc3s5h mentions was a historically important technique.

- Could someone please say a few words about it in the "history" section of Design For Test, which currently doesn't even mention it? --DavidCary (talk) 15:31, 18 August 2011 (UTC)

- DavidCary, "was a historically important technique" makes it sound as if you think it is no longer important. I know it was still going strong at IBM in 2001. Do you have any evidence that it has fallen out of use?